# Nonvolatile Memory Functionality of ZnO Nanowire Transistors Controlled by Mobile Protons

Jongwon Yoon,<sup>†</sup> Woong-Ki Hong<sup>†,§</sup> , Minseok Jo,<sup>†</sup> Gunho Jo,<sup>†</sup> Minhyeok Choe,<sup>†</sup> Woojin Park,<sup>†</sup> Jung Inn Sohn,<sup>‡</sup> Stanko Nedic,<sup>‡</sup> Hyungsang Hwang,<sup>†</sup> Mark E. Welland,<sup>‡</sup> and Takhee Lee<sup>†,\*</sup>

†School of Materials Science and Engineering, Department of Nanobio Materials and Electronics, Gwangju Institute of Science and Technology, Gwangju 500-712, Korea, and †Nanoscience Centre, University of Cambridge, Cambridge CB3 OFF, United Kingdom. <sup>§</sup>These authors contributed equally to this work.

**ABSTRACT** We demonstrated the nonvolatile memory functionality of ZnO nanowire field effect transistors (FETs) using mobile protons that are generated by high-pressure hydrogen annealing (HPHA) at relatively low temperature (400 °C). These ZnO nanowire devices exhibited reproducible hysteresis, reversible switching, and nonvolatile memory behaviors in comparison with those of the conventional FET devices. We show that the memory characteristics are attributed to the movement of protons between the Si/SiO<sub>2</sub> interface and the SiO<sub>2</sub>/ZnO nanowire interface by the applied gate electric field. The memory mechanism is explained in terms of the tuning of interface properties, such as effective electric field, surface charge density, and surface barrier potential due to the movement of protons in the SiO<sub>2</sub> layer, consistent with the UV photoresponse characteristics of nanowire memory devices. Our study will further provide a useful route of creating memory functionality and incorporating proton-based storage elements onto a modified CMOS platform for FET memory devices using nanomaterials.

**KEYWORDS:** ZnO nanowires  $\cdot$  field effect transistors  $\cdot$  nonvolatile memory mobile protons

he control and design of electronic properties in nanomaterial-based devices are of great importance not only for creating and exploring their novel electronic functions but also for their applications in several diverse fields, including electronics, 1 photonics, 2 chemical/biological sensing,<sup>3,4</sup> and solar energy conversion/ storage.<sup>5</sup> So far, to this end, a variety of strategies have been investigated by doping,<sup>6</sup> heterostructure design,<sup>7</sup> irradiation engineering,8 molecular functionalization techniques,<sup>9</sup> and interface engineering.<sup>10,11</sup> In particular, the interface manipulation of semiconductor devices has attracted significant attention because the operating principles and performance of these devices are critically affected by their interfacial properties. 11,12

Most importantly, nanoscale FET configurations provide a general platform to individually functionalize the surfaces of nanomaterial species within a nanoscale system. Such a transistor configuration en-

compasses a large surface-to-volume ratio, and the interfaces play a crucial role in defining the fundamental transport characteristics of these transistors, especially in regard to novel memory characteristics. 12-25 For example, the electrical transport behavior or the threshold voltage of nanoscale FETs can be tuned by controlling the interfacial properties through several methods, such as surface-architecture-controlled ZnO nanowire growth, 13 proton-irradiationassisted manipulation, 14,15 and mechanical strain. 16,17 In addition to tuning the fundamental FET properties, considerable efforts have been devoted to addressing the issues of creating memory functionality by forming functional interfacial areas through the use of electric double layers, 18 nanoparticles, 19 self-assembled molecules, 9,20 ferroelectric dielectric films, 21-23 and, particularly, mobile protons; 18,24,25 however, with regard to memory devices with mobile protons, the existing proton-generating approach at high temperatures (~1000 °C) can seriously induce undesirable effects on the materials and devices. Accordingly, the generation of mobile protons necessitates a low-temperature process as one of the key issues for the proton-based memory elements with an FET configuration. 18,24,25 Furthermore, for the wide application of the nanomaterial-based FETs beyond the FET generic function, manipulation of the interfacial properties through mobile protons for creating memory functions is very important. To the best of our knowledge, no previous work has demonstrated the nanomaterial-based memory transistors by using mobile protons generated particularly at the low temperature.

Herein, we have demonstrated that ZnO nanowire-based FETs have memory-

\*Address correspondence to tlee@gist.ac.kr.

Received for review October 4, 2010 and accepted December 7, 2010.

Published online December 14, 2010. 10.1021/nn102633z

© 2011 American Chemical Society

switching characteristics using mobile protons, which can be generated through a high-pressure hydrogen annealing (HPHA) at a relatively low temperature (400 °C). Our primary focus is to translate the generic FET function of the ZnO nanowire transistor into memory characteristics by employing mobile protons in the SiO<sub>2</sub> layer. We have observed that reversible memory characteristics are attributed to proton movement between the Si/SiO<sub>2</sub> interface and the SiO<sub>2</sub>/nanowire interface. Specifically, the memory characteristics of ZnO nanowire FETs can be described in terms of the effective electric field, surface charge density, and surface barrier potential at the nanowire surface, all of which depend on the movement of protons by the application of a gate electric field.

## **RESULTS AND DISCUSSION**

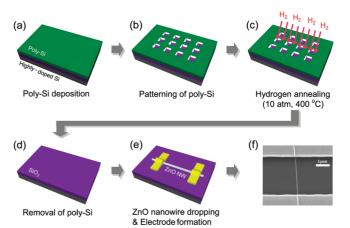

A fabrication scheme of a memory device based on a single ZnO nanowire FET and its field emission scanning electron microscopy (FESEM) image are illustrated in Figure 1. First, a 50 nm thick poly-Si film was deposited onto a highly doped p-type Si substrate with a thermally grown 100 nm thick SiO<sub>2</sub> layer by low-pressure chemical vapor deposition (LPCVD) (Figure 1a). Next, hole patterns with diameters of 100 µm were formed in the poly-Si film for the lateral diffusion of hydrogen molecules by photolithography and wet chemical etching using a mixed solvent of HNO<sub>3</sub>/HF/DI water (Figure 1b).<sup>24</sup> After the HPHA process (400 °C, 10 atm) of the patterned substrates for  $\sim$ 40 min (Figure 1c), the patterned poly-Si film was removed by KOH solution at 70 °C (Figure 1d). Subsequently, the ZnO nanowires grown by a vapor transport method were transferred to the Si substrates, and the FET devices were fabricated by photolithography and a lift-off process (Figure 1e). Figure 1f shows an FESEM image of a fabricated single ZnO nanowire FET device with a space of approximately 3 µm between two electrodes. Further detailed information of device fabrication is provided in the Experimental Methods.

A series of transfer characteristics (drain current versus gate voltage curves,  $I_{DS}-V_G$ ) and their corresponding memory hysteresis window were measured in an ambient atmosphere and at room temperature for the nanowire memory FET devices treated with HPHA (Figure 2a-c) and for the conventional nanowire FET device without the HPHA treatment (Figure 2d-f), respectively. The transfer curves in Figure 2a,d show the direction and hysteresis behavior with a double sweep of the gate voltage ( $V_G$ ) from -15 to 15 V at variable drain voltages ( $V_{DS} = 0.1, 0.4, 0.7, \text{ and } 1 \text{ V}$ ). Figure 2b,e shows the variation of the hysteresis memory window at the various sweep ranges of  $V_G$  at a fixed drain voltage ( $V_{DS} = 0.1 \text{ V}$ ). Interestingly, the nanowire memory FET devices exhibited a completely different behavior in comparison to the conventional nanowire FET devices. Specifically, the memory window of the nanowire memory FETs significantly increased with increasing

Figure 1. Fabrication process of a nanowire memory FET device. (a) The deposition of a 50 nm thick poly-Si film on a SiO<sub>2</sub> layer. (b) Hole patterning in the poly-Si film. (c) Hydrogen annealing at 400 °C and 10 atm. (d) Removal of the poly-Si film. (e) The fabrication of a ZnO nanowire FET device. (f) An FESEM image of a fabricated device.

gate voltage sweep ranges, whereas the conventional FETs did not exhibit any noticeable hysteresis behavior in their  $I_{DS} - V_G$  characteristics. To allow for statistical descriptions of the hysteresis width as a function of the  $V_{\rm G}$  sweep range, a total of 14 nanowire FET devices were characterized: 7 devices for the nanowire memory FETs (Figure 2c) and 7 devices for the conventional nanowire FETs (Figure 2f). The hysteresis widths of the nanowire memory FET devices exhibited much stronger linear dependence on the  $V_G$  sweep range than those of conventional FET devices. The hysteresis widths of the

Figure 2. Electrical characteristics of (a-c) the nanowire memory devices and (d-f) the conventional nanowire devices without the HPHA process. (a, d)  $I_{DS}-V_G$  curves of a representative device that exhibits the hysteretic behavior (at  $V_{DS} = 0.1, 0.4, 0.7, \text{ and } 0.1 \text{ V}$ ). (b, e) Hysteresis window width variation with increasing  $V_G$  sweep range in  $I_{DS}-V_G$  curves (at  $V_{DS}=0.1$  V). (c, f) The statistical spread of the hysteresis window widths as a function of the  $V_G$  sweep range.  $V_G$  sweep rate =  $\sim$ 3 V/s.

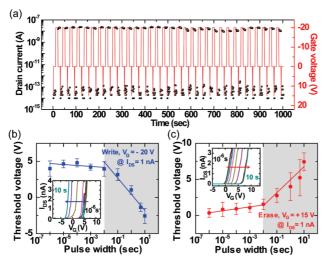

Figure 3. Representative ON/OFF switching characteristics and the statistical data of threshold voltage shifts as a function of pulse width for the nanowire memory devices. (a) The ON and OFF states measured at the read voltage ( $V_{\rm G}=0$  V) after write pulses of -20 V for 10 s and an erase pulse of 15 V for 1 s were applied, respectively. The threshold voltage shift as a function of pulse width for (b) the write operation ( $V_{\rm G}=-20$  V) and (c) the erase operation ( $V_{\rm G}=15$  V). The insets show the representative  $I_{\rm DS}-V_{\rm G}$  curves that derive from the application of write (b) and erase (c) pulses with increasing pulse widths, respectively.

nanowire memory FETs were observed to be 3.0  $\pm$  2.6, 9.4  $\pm$  3.5, 15.7  $\pm$  4.3, and 20.7  $\pm$  6.7 for the  $V_{\rm G}$  sweep ranges of 15 V (from -10 to 5 V), 25 V (from -15 to 10 V), 35 V (from -20 to 15 V), and 45 V (from -25 to 20 V), respectively. Note that the hysteresis width was somewhat arbitrarily defined as the difference in the gate voltage at which the drain current (I<sub>DS</sub>) is 1 nA during the forward and reverse sweeps (Figure 2a,d). It is well known that the hydrogen annealing can generate protons in a SiO<sub>2</sub> layer through hydrogen diffusion in the poly-Si/SiO<sub>2</sub>/Si configuration and that the generated protons have mobile characteristics that depend on the applied gate electric field.<sup>24</sup> Therefore, this result suggests that the movement of protons by the application of a gate bias enables the ZnO nanowire FET to exhibit reproducible hysteresis loops.

To investigate the hysteretic nature of nanowire memory FET devices as a potential memory operation, the fabricated transistors were biased with a negative gate voltage ( $V_G = -20 \text{ V}$ , write) and a positive gate voltage ( $V_G = 15 \text{ V}$ , erase). Figure 3a displays the representative data of the reversible ON/OFF switching characteristics of a nanowire memory FET device for pulse signals of  $V_G = -20$  and +15 V at  $V_{DS} = 0.1$  V (also see Figure S1 in the Supporting Information for pulse signals of  $V_G = \pm 15$  V at  $V_{DS} = 0.1$  V). Here, the interesting result is that, after the application of the write and erase voltage pulses, two memory states, a high conductance (ON state) and a low conductance (OFF state) at  $V_G = 0$  V, were achieved. Importantly, the reversible conductance modulation of the nanowire memory devices implies that the generated protons can repeatedly move between the Si/SiO<sub>2</sub> interface and the SiO<sub>2</sub>/ZnO

nanowire interface with alternating gate bias polarity. Figure 3b,c shows the distribution of the threshold voltage (defined here as the gate voltages at  $I_{DS} = 1 \text{ nA}$ ) as a function of pulse width for four different devices and the corresponding representative  $I_{DS}-V_{G}$  data (the insets of Figure 3b,c) for the application of the write pulse (-20 V) and the erase pulse (+15 V), respectively. The pulse time dependencies of the threshold voltage  $(V_{th})$  shift show two different slopes for both the write and the erase operations. Specifically, when applying a short time pulse (from 1  $\mu$ s to 10 ms), the  $V_{th}$  shift exhibited a weak dependency on the pulse time (with less steep slopes), whereas when applying a relatively longer time pulse (>10 ms), the  $V_{th}$  shift exhibited a strong dependency on the pulse time (with much steeper slopes). This indicates that the  $V_{th}$  shift is related to the write/erase time scale required to move the protons through the SiO<sub>2</sub> layer (100 nm). Therefore, the switching speed of the nanowire memory FETs is also limited by the movement of mobile protons, which depends on the oxide thickness ( $t_{ox}$ ) and the gate voltage  $(V_G)$ . The rate of proton motion across the SiO<sub>2</sub> layer is proportional approximately to  $V_G^2$  and  $t_{ox}^{-3}$ .<sup>24</sup> This indicates that write and erase speeds for the devices with a relatively thicker (100 nm) SiO<sub>2</sub> layer are much slower than those in devices with a thinner ox-

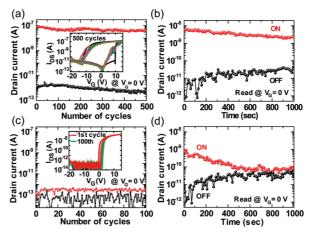

In addition to the reversible switching characteristics, we investigated the endurance and retention characteristics of the nanowire memory FETs in order to elucidate the memory functionality that results from the mobile proton-induced hysteresis behavior, compared with the case for the conventional nanowire FETs. Figure 4a,c shows device endurance as a function of the ON/OFF cycles for the nanowire memory FETs and the conventional nanowire FETs, respectively. Here, we observed that the nanowire memory devices exhibit highly reproducible hysteresis loops with wellseparated ON and OFF states for hundreds of cycles without degradation at the read voltage ( $V_G = 0 \text{ V}$  at  $V_{\rm DS} = 0.1 \text{ V}$ ) (Figure 4a), whereas the conventional nanowire FETs exhibit no memory window between both the ON and the OFF states during the measured hundred cycles. The retention characteristics of the nanowire memory and conventional devices were also measured at the read voltage ( $V_G = 0 \text{ V}$ ) after applying a gate bias pulse of -20 V for 10 s (ON state) and +15 Vfor 1 s (OFF state), as shown in Figure 4b,d, respectively. Interestingly, for the nanowire memory FET devices, the ON and OFF states were well-maintained up to 1000 s in comparison to the conventional nanowire FET devices. Note that the large driving voltages and poor retention properties may be related to the nature of mobile protons in the thick SiO<sub>2</sub> layer (100 nm). Nevertheless, this study can be a proof-of-concept of the nonvolatile memory functionality of the ZnO nanowire FETs.

It is well known that ZnO nanowire FETs are highly sensitive to the presence and nature of adsorbed surface species, such as oxygen or water molecules.<sup>26,27</sup> For example, the influence of the measurement environment has been previously observed to play a dramatic role on the transport properties of ZnO nanowire FETs. In particular, the threshold voltage ( $V_{th}$ ) shift and hysteresis in electrical properties of ZnO nanowire FET devices can be caused by the adsorbed molecules. 15,28 Therefore, to investigate whether the observed nonvolatile memory behavior is influenced by water and gas molecules in air environment, we further studied the hysteresis and retention properties of a nanowire memory FET in a N<sub>2</sub>-filled environment. We similarly observed a remarkable hysteresis memory window and a well-maintained data retention characteristic for the nanowire memory devices in comparison to those in an air environment (see Figure S3 in the Supporting Information). Accordingly, we believe that the nonvolatile memory functions primarily originate from the mobile proton-induced interface effects, but not simply from water or other gas molecules.

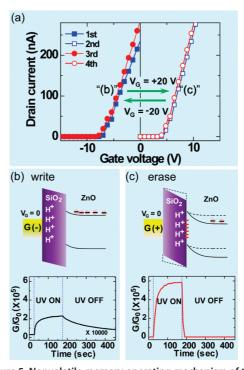

The operating mechanism of nanowire memory FETs can be explained by the equilibrium energy band diagrams that correspond to the write/erase operations in the reversible electrical transport properties ( $I_{DS}-V_{G}$ ), which was characterized after a polychloro-paraxylylene (parylene-C) passivation layer was coated so as to effectively remove the influences of gas molecules, such as water or oxygen molecules. 13,15,29 Figure 5a shows the reversible transfer characteristics  $(I_{DS}-V_G)$  of the nanowire memory devices with a high conductance state (ON state, denoted as (b)) and a low conductance state (OFF state, denoted as (c)) at the read voltage ( $V_G = 0 \text{ V}$ ) after applying gate bias pulses of -20and +20 V, respectively. The operation mode of the devices switched from a write operation into an erase operation after a positive gate bias pulse ( $V_G = 20 \text{ V}$ ) was applied and reversely switched from an erase operation into a write operation after a negative gate bias pulse  $(V_G = -20 \text{ V})$  was applied. The equilibrium energy band diagrams of a nanowire memory device that correspond to the write operation (ON state) and the erase operation (OFF state) in the  $I_{DS} - V_G$  curves (Figure 5a) are shown in Figure 5b,c, respectively. For the write operation (ON state), the mobile protons move to the Si/ SiO<sub>2</sub> interface after the application of a negative gate bias pulse, resulting in an enhancement of the effective gate electric field. Such a constructive electric field leads to an increase in the channel conductance, a smaller surface depletion, and a relatively lower surface barrier potential at the SiO<sub>2</sub>/ZnO nanowire interface (Figure 5b, top). In contrast, for the erase operation (OFF state), the mobile protons move toward the SiO<sub>2</sub>/ZnO nanowire interface after the application of a positive gate bias pulse, resulting in the electrostatic capture of electrons at the ZnO nanowire surface (Figure 5c, top). The formation of such interface states can

Figure 4. (a, c) Endurance characteristics of a nanowire memory device and a conventional nanowire FET at the read voltage (V<sub>G</sub> = 0 V at  $V_{DS}$  = 0.1 V), respectively. (b, d) Retention characteristics of a nanowire memory device and a conventional nanowire FET at the read voltage ( $V_G = 0 \text{ V}$  at  $V_{DS} = 0.1 \text{ V}$ ) after the application of a write pulse (-20 V, 10 s) and an erase pulse (+15 V, 1 s) respectively. The insets show the hysteresis curves that result from double sweeps of the gate voltage in endurance tests.

reduce the number of free electron carriers of the ZnO surface, as well as create a relatively larger surface depletion width and a higher surface barrier potential, resulting in a shift of the threshold voltage toward the positive gate bias direction and conductance modulation.

Correspondingly, the memory-switching behavior of the nanowire memory FETs can be explained by

Figure 5. Nonvolatile memory operating mechanism of the nanowire memory devices. (a) Reversible  $I_{DS} - V_G$  characteristics after the application of write ( $V_G = -20 \text{ V}$ ) and erase  $(V_G = +20 \text{ V})$  pulses. (b, c) The energy band diagrams at  $V_G$ = 0 V after applying write/erase pulses (top) and UV photoresponse characteristics (bottom) that correspond to (b) write and (c) erase operations.

quantitatively considering the concentration of mobile protons, the electrostatically trapped charge concentration, and the effective gate electric field. First, according to secondary ion mass spectroscopy (SIMS) data (Figure S4 in the Supporting Information), the concentration of mobile protons per unit area in the SiO<sub>2</sub> layer can be estimated to be on the order of  $\sim 10^{12}$  cm<sup>-2</sup>, which is consistent with previously reported values.<sup>24,30</sup> In addition, as shown in Figure 5a, changes in threshold voltages ( $\Delta V_{\rm th} = \sim 11.5$ ) can be used to calculate the change in carrier concentration per unit area ( $\Delta n_e$ ). Here, for convenience of discussion and simplification, we assume that the  $\Delta n_e$  is equivalent to the electrostatically trapped charge concentration  $(N_{it})$  per unit area at the SiO<sub>2</sub>/ZnO nanowire interface using the following equations 13,15,31,32

$$q\Delta n_{\rm e} = \frac{C_{\rm g}\Delta V_{\rm th}}{2\pi rL} \approx qN_{\rm it} \tag{1}$$

$$C_{\rm g} = \frac{2\pi\varepsilon_{\rm SiO_2}L}{\cosh^{-1}\left(1 + \frac{h}{r}\right)} \tag{2}$$

where  $C_{\rm g}$  is the gate capacitance, r is the nanowire radius (50 nm), L is the nanowire channel length (3  $\mu$ m), h is the SiO<sub>2</sub> thickness (100 nm), and  $\varepsilon_{\rm SiO_2}$  is the permittivity of SiO<sub>2</sub> (3.9). Thus, the  $N_{\rm it}$  can be estimated to be  $\sim 2.8 \times 10^{12}$  cm<sup>-2</sup>, which is comparable to the concentration of the mobile protons that was determined via SIMS characterization. These data indicate that the positively charged protons can capture the electrons electrostatically at the SiO<sub>2</sub>/ZnO nanowire interface. These trapped charges at the interface can be expressed as  $^{13,15,31}$

$$\Delta Q_{\rm d} = -\sqrt{2\epsilon_{\rm 7DO}qN_{\rm d}\Delta\phi_{\rm S}} = -qN_{\rm it} \tag{3}$$

where  $\Delta Q_{\rm d}$  is the change in the depleted amount of areal charge density in the ZnO nanowire,  $\epsilon_{\rm ZnO}$  is the permittivity of ZnO (8.66),  $N_{\rm d}$  is the doping concentration, and  $\Delta \varphi_{\rm S}$  is the change in the surface barrier potential. In addition, the effective gate electric field at the ZnO nanowire surface can be calculated from the following equation  $^{15,33,34}$

$$\xi_{\text{eff}} = \frac{1}{\varepsilon_{\text{ZnO}}} \left( \frac{1}{2} Q_{\text{tot}} + Q_{\text{d}} \right) \tag{4}$$

where  $Q_{tot}$  is the total areal charge density in the ZnO nanowire channel. Here, if we assume  $\varphi_S=0.01$  V (for the write operation) and  $N_d=5\times 10^{17}$  cm<sup>-3</sup> as typical values, then we can obtain  $\varphi_S=0.42$  V (for the erase operation) and  $\zeta_{eff}=0.87$  and 0.03 MV/cm at  $V_G=10$

V for the write and erase operations, respectively, using eqs 1–4 (also see Figure S5 in the Supporting Information). This implies that the nonvolatile memoryswitching behavior in the nanowire memory FETs is caused by the modulation of the interfacial properties, including the effective gate electric field, surface charge density, and surface barrier potential.

Furthermore, to unambiguously explain the impact of the electrostatically trapped charges at the SiO<sub>2</sub>/ ZnO nanowire interface due to mobile protons, we investigated the UV photoresponse of a nanowire memory device that corresponds to the write operation (ON state) and the erase operation (OFF state) in the  $I_{DS}-V_{G}$  curves (Figure 5b,c, bottom, respectively). Note that the normalized photoconductance response was plotted for the ratio of the conductance measured when the UV was on (G) and off ( $G_0$ ). Interestingly, as shown in the photoconductance responses (Figure 5b,c, bottom; also see Figure S6 in the Supporting Information), we found that the UV sensitivity of the ZnO nanowire for the erase operation was much higher than that for the write operation. This is likely caused by the negative interface states arising from the electrons trapped electrostatically by the protons that moved toward the SiO<sub>2</sub>/ZnO nanowire interface after the application of a positive gate bias pulse. The presence of the negatively charged species, such as oxygen molecules or immobilized electrons, highly sensitize the UV detection of a ZnO nanowire. 35,36 Similarly, upon UV illumination, the electrons that are electrostatically trapped by the positively charged protons can act as photongenerated hole-trapping states, resulting in a highly sensitive UV response. It is immediately apparent that the modulation of the interfacial properties is caused by the movement of protons via the applied gate electric field, resulting in the nonvolatile functionality of ZnO nanowire FETs.

# CONCLUSION

In summary, we have fabricated the ZnO nanowire-based nonvolatile memory FETs using mobile protons, which can be generated by the high-pressure hydrogen annealing (HPHA) at low temperature (400 °C). The nanowire memory FET devices exhibited reproducible hysteresis behavior, stable ON/OFF switching, and nonvolatile memory characteristics. The memory functionality of ZnO nanowire transistors can be explained in terms of the modulation of interfacial properties, such as the effective gate electric field, surface charge density, and surface barrier potential, due to the movement of protons in the  $\mathrm{SiO}_2$  layer that is caused by the application of a gate electric field.

# **EXPERIMENTAL METHODS**

**Device Fabrication.** The detailed method of ZnO nanowire growth by vapor transport and the general fabrication method of nanowire FETs are described elsewhere.<sup>13</sup> To generate mobile

protons in the  $SiO_2$  layer (100 nm), the hole patterned substrate (poly-Si (50 nm)/SiO<sub>2</sub> (100 nm)/highly doped p-type Si substrate) was placed into a chamber and annealed in pure hydrogen environment under a pressure of 10 atm and at a temperature of

400 °C for 40 min. After the substrates were annealed, the chamber was cooled at the room temperature.

Passivation Layer Coating. To effectively remove the influence of water or gas molecules in ambient air, a passivation layer of parylene-C film (dielectric constant  $\varepsilon =$  3.1 at 1 kHz) was deposited on fabricated devices at room temperature by vacuum sublimation in a special coating system (Labcoater 2010, U.K.).<sup>2</sup>

Device Characterization. The measurement of the memory characteristics for the fabricated devices was carried out using a semiconductor parameter analyzer, HP 4145C. In addition, a Keithley 4200 semiconductor characterization system was used to measure the electrical characteristics of nanowire FETs in a N<sub>2</sub>filled ambient, as well as their UV photoresponse.

Acknowledgment. This work was supported by the National Research Laboratory program; a National Core Research Center Grant; the World Class University Program of the Korean Ministry of Education, Science and Technology; and the Program for Integrated Molecular Systems at GIST. W.-K.H., J.I.S., and M.E.W. were supported by the European Union through the FP7 Project Nabab (Contract FP7-216777).

Supporting Information Available: ON/OFF switching, nonvolatile characteristics in N<sub>2</sub>-filled ambient, and UV photoresponse of ZnO nanowire memory devices; quantitative estimation of surface barrier potential, surface charge density, and effective electric field for the device; and hydrogen depth profile using secondary ion mass spectroscopy (SIMS). This material is available free of charge via the Internet at http://pubs.acs.org.

### REFERENCES AND NOTES

- 1. Lu, W.; Lieber, C. M. Nanoelectronics from the Bottom up. Nat. Mater. 2007, 6, 841-850.

- Yan, R.; Gargas, D.; Yang, P. Nanowire Photonics. Nat. Photonics 2009, 3, 569-576.

- Patolsky, F.; Zheng, G.; Lieber, C. M. Nanowire Sensors for Medicine and the Life Sciences. Nanomedicine 2006, 1, 51-65

- Schedin, F.; Geim, A. K.; Morozov, S. V.; Hill, E. W.; Blake, P.; Katsnelson, M. I.; Novoselov, K. S. Detection of Individual Gas Molecules Adsorbed on Graphene. Nat. Mater. 2007, 6,

- 5. Liu, J.; Cao, G.; Yang, Z.; Wang, D.; Dubois, D.; Zhou, X.; Graff, G. L.; Pederson, L. R.; Zhang, J.-G. Oriented Nanostructures for Energy Conversion and Storage. ChemSusChem 2008, 1, 676-697.

- 6. Ho, J. C.; Yerushalmi, R.; Jacobson, Z. A.; Fan, Z.; Alley, R. L.; Javey, A. Controlled Nanoscale Doping of Semiconductors via Molecular Monolayers. Nat. Mater. 2008, 7, 62-67.

- 7. Xiang, J.; Lu, W.; Hu, Y.; Wu, Y.; Yan, H.; Lieber, C. M. Ge/Si Nanowire Heterostructures as High-Performance Field-Effect Transistors. Nature 2006, 441, 489-493.

- 8. Krasheninnikov, A. V.; Banhart, F. Engineering of Nanostructured Carbon Materials with Electron or Ion Beams. Nat. Mater. 2007, 6, 723-733.

- 9. Li, C.; Fan, W.; Straus, D. A.; Lei, B.; Asano, S.; Zhang, D.; Han, J.; Meyyappan, M.; Zhou, C. Charge Storage Behavior of Nanowire Transistors Functionalized with Bis(terpyridine)-Fe(II) Molecules: Dependence on Molecular Structure. J. Am. Chem. Soc. 2004, 126, 7750-7751.

- 10. Chen, L.-M.; Xu, Z.; Hong, Z.; Yang, Y. Interface Investigation and Engineering-Achieving High Performance Polymer Photovoltaic Devices. J. Mater. Chem. 2010, 20, 2575-2598.

- 11. Ma, H.; Yip, H.-L.; Huang, F.; Jen, A. K.-Y. Interface Engineering for Organic Electronics. Adv. Funct. Mater. **2010**, 20, 1371-1388.

- 12. Agarwal, R. Heterointerfaces in Semiconductor Nanowires. Small 2008, 4, 1872-1893.

- 13. Hong, W.-K.; Sohn, J. I.; Hwang, D.-K.; Kwon, S.-S.; Jo, G.; Song, S.; Kim, S.-M.; Ko, H.-J.; Park, S.-J.; et al. Tunable **Electronic Transport Characteristics of Surface-**Architecture-Controlled ZnO Nanowire Field Effect Transistors. Nano Lett. 2008, 8, 950-956.

- 14. Jo, G.; Hong, W.-K.; Sohn, J. I.; Jo, M.; Shin, J.; Welland, M. E.; Hwang, H.; Geckeler, K. E.; Lee, T. Hybrid Complementary Logic Circuits of One-Dimensional Nanomaterials with Adjustment of Operation Voltage. Adv. Mater. 2009, 21, 2156-2160.

- 15. Hong, W.-K.; Jo, G.; Sohn, J. I.; Park, W.; Choe, M.; Wang, G.; Kahng, Y. H.; Welland, M. E.; Lee, T. Tuning of the Electronic Characteristics of ZnO Nanowire Field Effect Transistors by Proton Irradiation. ACS Nano 2010, 4, 811-

- Wang, X.; Zhou, J.; Song, J.; Liu, J.; Xu, N.; Wang, Z. L. Piezoelectric Field Effect Transistor and Nanoforce Sensor Based on a Single ZnO Nanowire. Nano Lett. 2006, 6, 2768-2772.

- 17. Hu, Y.; Zhang, Y.; Chang, Y.; Snyder, R. L.; Wang, Z. L. Optimizing the Power Output of a ZnO Photocell by Piezopotential. ACS Nano 2010, 4, 4220-4224.

- Yuan, H.; Shimotani, H.; Tsukazaki, A.; Ohtomo, A.; Kawasaki, M.; Iwasa, Y. Hydrogenation-Induced Surface Polarity Recognition and Proton Memory Behavior at Protic-Ionic-Liquid/Oxide Electric-Double-Layer Interfaces. J. Am. Chem. Soc. 2010, 132, 6672-6678.

- 19. Faber, H.; Burkhardt, M.; Jedaa, A.; Kälblein, D.; Klauk, H.; Halik, M. Low-Temperature Solution-Processed Memory Transistors Based on Zinc Oxide Nanoparticles. Adv. Mater. 2009, 21, 3099-3104.

- Duan, X.; Huang, Y.; Lieber, C. M. Nonvolatile Memory and Programmable Logic from Molecule-Gated Nanowires. Nano Lett. 2002, 2, 487-490.

- 21. Yoon, S.-M.; Yang, S.; Byun, C.; Park, S.-H.; Cho, D.-H.; Jung, S.-W.; Kwon, O.-S.; Hwang, C.-S. Fully Transparent Non-Volatile Memory Thin-Film Transistors Using an Organic Ferroelectric and Oxide Semiconductor Below 200 °C. Adv. Funct. Mater. 2010, 20, 921-926.

- 22. Lee, K. H.; Lee, G.; Lee, K.; Oh, M. S.; Im, S. Flexible Low Voltage Nonvolatile Memory Transistors with Pentacene Channel and Ferroelectric Polymer. Appl. Phys. Lett. 2009, 94, 093304.

- 23. Liao, L.; Fan, H. J.; Yan, B.; Zhang, Z.; Chen, L. L.; Li, B. S.; Xing, G. Z.; Shen, Z. X.; Wu, T.; Sun, X. W.; et al. Ferroelectric Transistors with Nanowire Channel: Toward Nonvolatile Memory Applications. ACS Nano 2009, 3, 700-706.

- Vanheusden, K.; Warren, W. L.; Devine, R. A. B.; Fleetwood, D. M.; Schwank, J. R.; Shaneyfelt, M. R.; Winokur, P. S.; Lemnios, Z. J. Non-Volatile Memory Device Based on Mobile Protons in SiO<sub>2</sub> Thin Films. *Nature* **1997**, 386, 587–

- 25. Kapetanakis, E.; Douvas, A. M.; Velessiotis, D.; Makarona, E.; Argitis, P.; Glezos, N.; Normand, P. Molecular Storage Elements for Proton Memory Devices. Adv. Mater. 2008, 20, 4568-4574.

- 26. Goldberger, J.; Sirbuly, D. J.; Law, M.; Yang, P. ZnO Nanowire Transistors. J. Phys. Chem. B 2005, 109, 9-14.

- 27. Fan, Z.; Wang, D.; Chang, P.-C.; Tseng, W.-Y.; Lu, J. G. ZnO Nanowire Field-Effect Transistor and Oxygen Sensing Property. Appl. Phys. Lett. 2004, 85, 5923.

- Song, S.; Hong, W.-K.; Kwon, S.-S.; Lee, T. Passivation Effects on ZnO Nanowire Field Effect Transistors under Oxygen, Ambient, and Vacuum Environments. Appl. Phys. Lett. 2008, 92, 263109.

- 29. Sekitani, T.; Someya, T. Stretchable, Large-Area Organic Electronics. Adv. Mater. 2010, 22, 2228-2246.

- 30. Devine, R. A. B. Comparitive Behavior of Radiation and Thermally Generated Protons in Amorphous SiO<sub>2</sub>. J. Appl. Phys. 2001, 89, 2246-2250.

- Taur, Y.; Ning, T. H. Fundamentals of Modern VLSI Devices; Cambridge University Press: Cambridge, U.K., 1998; pp 117-125.

- 32. Gupta, D.; Anand, M.; Ryu, S.-W.; Choi, Y.-K.; Yoo, S. Non-Volatile Memory Based on Sol-Gel ZnO Thin-Film Transistors with Ag Nanoparticles Embedded in the ZnO/ Gate Insulator Interface. Appl. Phys. Lett. 2008, 93, 224106.

- Hairapetian, A.; Gitlin, D.; Viswanathan, C. R. Low-Temperature Mobility Measurements on CMOS Devices. IEEE Trans. Electron Devices 1989, 36, 1448-1455.

# ARTICLE

- 34. Takagi, S.; Toriumi, A.; Iwase, M.; Tango, H. On the Universality of Inversion Layer Mobility in Si MOSFET's: Part I-Effects of Substrate Impurity Concentration. *IEEE Trans. Electron Devices* **1994**, *41*, 2357–2362.

- Soci, C.; Zhang, A.; Xiang, B.; Dayeh, S. A.; Aplin, D. P. R.; Park, J.; Bao, X. Y.; Lo, Y. H.; Wang, D. ZnO Nanowire UV Photodetectors with High Internal Gain. *Nano Lett.* 2007, 7, 1003–1009.

- Lao, C. S.; Park, M.-C.; Kuang, Q.; Deng, Y.; Sood, A. K.; Polla, D. L.; Wang, Z. L. Giant Enhancement in UV Response of ZnO Nanobelts by Polymer Surface-Functionalization. J. Am. Chem. Soc. 2007, 129, 12096–12097.